## Eight 4:1 multiplexers with serial interface and LNA

PR2530 contains eight 4:1 mulitplexers in one chip. By connecting several chips in series, the number of channels can be further increased. The main application is for the receiving part of imaging ultrasound instruments.

In addition to the multiplexer, it contains a lownoise amplifier for each channel, to drive the load of a cable with parasitic capacitance.

#### **FEATURES**

- 8 channels with 4:1 multiplexers

- independently switchable inputs, allowing to group several inputs to one output

- cascadable serial interface

- AC coupled input

- output buffered by LNA

- supply voltage 3.3V

### **APPLICATIONS**

• Imaging ultrasound systems

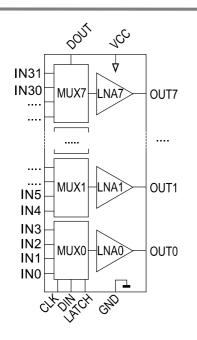

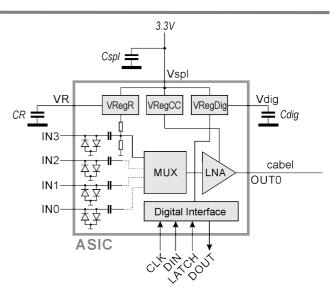

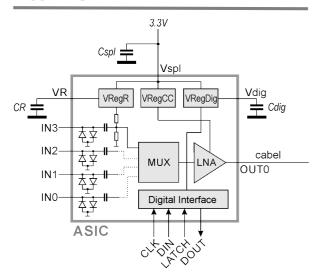

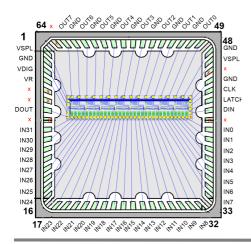

#### **BLOCK DIAGRAM**

Left: diagram of whole chip

Right: detailed diagram of one 4:1 MUX

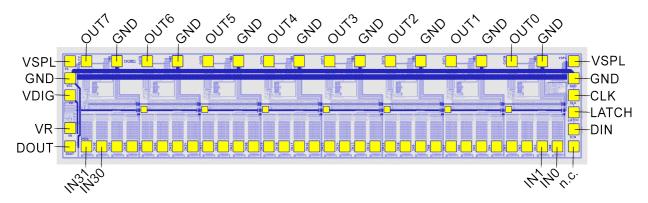

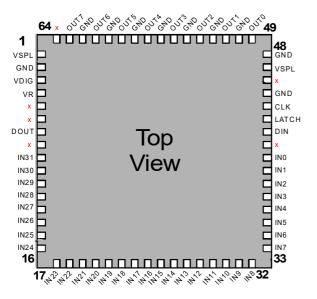

#### **PIN DESCRIPTION**

| Pin No | Pin Name | Pin Function Description    |

|--------|----------|-----------------------------|

| 1      | VSPL     | supply voltage              |

| 2      | Gnd      | ground connection           |

| 3      | VDIG     | connection to reservoir cap |

| Pin No | Pin Name     | Pin Function Description                             |  |  |

|--------|--------------|------------------------------------------------------|--|--|

|        |              | for digital supply                                   |  |  |

| 4      | VR           | connection to reservoir cap<br>for reference voltage |  |  |

| 5-6    | n.c.         | no connection                                        |  |  |

| 7      | DOUT         | output of shift register                             |  |  |

| 8      | n.c.         | no connection                                        |  |  |

| 9-40   | IN31 INO     | input channel 31 0                                   |  |  |

| 41     | n.c.         | no connection                                        |  |  |

| 42     | DIN          | serial register data input                           |  |  |

| 43     | LATCH        | serial register data latch                           |  |  |

| 44     | CLK          | serial register data clock                           |  |  |

| 45     | GND          | ground connection                                    |  |  |

| 46     | n.c.         | no connection                                        |  |  |

| 47     | VSPL         | supply voltg (connect with pin 1)                    |  |  |

| 48-63  | GND          | ground connection                                    |  |  |

| 49-64  | OUTO<br>OUT7 | output from LNAs                                     |  |  |

## **Properties**

### **BLOCK DIAGRAM**

Each block (4 inputs, 1 output) contains

- an input limiter, clamping the signal to  $\pm 0.7V$

- a coupling capacitor and following DC bias source

- a 4:1 multiplexer, controlled by the digital interface

- a low-noise amplifier

The circuit blocks are supplied from the 3.3V power supply via internal voltage regulators. To smoothen the voltage, a reservoir capacitor should be connected to Vspl, VR and Vdig. This prevents e.g. a distortion of the reference voltage by the pulsing digital supply signal.

d

## **ELECTRICAL CHARACTERISTICS**

Ta = 25°C, unless otherwise noted.

| Symbol             | Parameter                                        | Conditions    | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------|---------------|------|------|------|-------|

| $V_{SPL}$          | Supply voltage                                   |               | 3.0  | 3.3  | 3.6  | V     |

| I <sub>SPL</sub>   | Supply current                                   |               |      |      | 20   | mA    |

| V <sub>clamp</sub> | Input clamping voltage                           |               | -0.7 |      | 0.7  | V     |

| l <sub>in</sub>    | Input current                                    |               |      |      | 0.5  | mA    |

|                    | DC voltage level after coupling capacitor        |               | 1.14 | 1,20 | 1.26 | V     |

|                    | DC offset between channels within one group of 4 |               | -1%  |      | +1%  |       |

|                    | DC offset between channels of different groups   |               | -2%  |      | 2%   |       |

| Z <sub>inp</sub>   | Input impedance                                  |               | 100  |      |      | kΩ    |

|                    | Attenuation input > MUX out                      | switch open   | 60   |      |      | dB    |

|                    | Attenuation input > MUX out                      | switch closed |      |      | ]*   | dB    |

|                    | Transmitted signal frequency                     |               | 1    |      | 6    | MHz   |

|                    | Attenuation between adjacent channels            |               | 60   |      |      | dB    |

| Ta                 | Ambient temperature                              |               | 0    |      | 60   | °C    |

$<sup>^{\</sup>star}$  The attenuation with closed switch depends on the frequency and parasitic input resistances and capacitances.

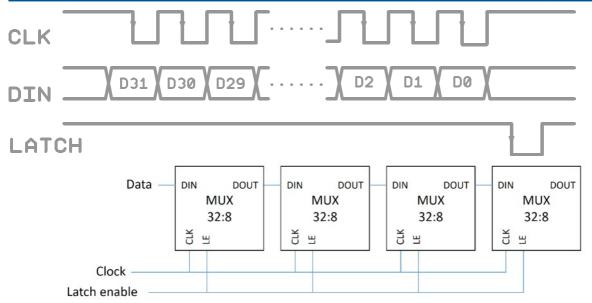

## **DIGITAL INTERFACE**

| Symbol | Parameter                                           | Min                    | Тур | Max           | Units |

|--------|-----------------------------------------------------|------------------------|-----|---------------|-------|

|        | Logic Input High Level (DIN, CLK, LATCH)            | 1.0                    |     | 6.0           | V     |

|        | Logic Input Low Level (DIN, CLK, LATCH)             | 0                      |     | 0.4           | V     |

|        | Logic Input Capacitance (DIN, CLK, LATCH)           |                        |     | 10            | рF    |

|        | Logic Output High Level (DOUT) @ Iout = 50µA        | V <sub>spl</sub> - 0.2 |     | $V_{\sf spl}$ | V     |

|        | Logic Output Low Level (DOUT) @ $I_{out} = 50\mu A$ | 0                      |     | 0.2           | V     |

|        | Logic Output Current (DOUT)                         | 0.1                    |     |               | mA    |

|        | Clock Period                                        |                        | 50  |               | ns    |

|        | Clock High Time                                     |                        | 25  |               | ns    |

|        | Clock Low Time                                      |                        | 25  |               | ns    |

|        | Data Setup Time                                     |                        | 10  |               | ns    |

|        | Data Hold Time                                      |                        | 5   |               | ns    |

|        | Clock to Latch Time                                 | 75                     |     |               | ns    |

|        | Latch High Time                                     | 50                     |     |               | ns    |

### LNA

| Symbol | Parameter                            | Condition | Min  | Тур  | Max  | Units |

|--------|--------------------------------------|-----------|------|------|------|-------|

|        | Output voltage                       | Vin = 0   | 1.14 | 1.20 | 1.26 | V     |

|        | Output voltage range                 |           | 0.1  |      | 2.0  | V     |

|        | Frequency range                      |           | 1    |      | 5    | MHz   |

|        | Output impedance                     | @3MHz     |      |      | 20   | Ohm   |

|        | Load resistance connected to output  |           | 500  |      |      | Ohm   |

|        | Load capacitance connected to output |           |      |      | 100  | pF    |

|        | Gain                                 |           |      | ±10  |      | dB    |

## Performance

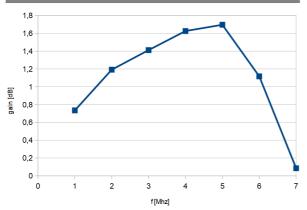

### TRANSFER FUNCTION

The transfer function is limited by the AC coupling at low frequencies, and by the LNA at high frequencies.

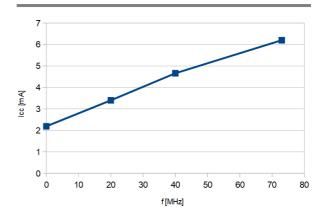

### **SUPPLY CURRENT FOR SHIFT REGISTER**

Digital supply current vs. clock frequeny of shift register

## Package Dimensions

Package: QFN 9.0  $\times$  9.0 All parts are RoHS compliant. Finish is pure tin. Detailed package information on request.

This integrated circuit has been developed as part of the joint research project "ULTRAWEAR" (Ultrasound-based Wearable as biofeedback system for effective muscle training in chronic dorsal pain). The project was financially supported by the Federal Ministry for Education and Research, Germany, and DLR.

### Disclaimer

Information provided by PREMA is believed to be accurate and correct. However, no responsibility is assumed by PREMA for its use, nor for any infringements of patents or other rights of third parties which may result from its use. PREMA reserves the right at any time without notice to change circuitry and specifications.

#### Life Support Policy

PREMA Semiconductors products are not authorized for use as critical components in life support devices or systems without the express written approval of PREMA Semiconductor. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### PREMA Semiconductor GmbH

Robert-Bosch-Str. 6 55129 Mainz Germany Phone: +49-6131-5062-0 Fax: +49-6131-5062-220

Email: <u>prema@prema.com</u> Web site: www.prema.com